# **Enhancement Mode N-Channel Power MOSFET**

PDFN5X6/NMOS/100V/ $\pm$ 20V/1.5V/35A/21.8m $\Omega$

Rev<sub>0.5</sub>

## 100V, 21.8mΩ, 35A, N-Channel Enhancement MOSFET

#### 1.Features

- ◆ 100V MOSFET technology

- ◆ Low on-state resistance

- Fast switching

- ♦ Vgs±20V

- ◆ 100% RG Tested

- ◆ 100% UIS Tested

| 2.Applications | lications | 2.App |

|----------------|-----------|-------|

|----------------|-----------|-------|

- Power Switching Application

- ◆ Load Switching

| V <sub>DS</sub> | R <sub>DS(on)</sub> Typ. | I <sub>D</sub> Max. |

|-----------------|--------------------------|---------------------|

| 400)/           | 21.8mΩ @ 10V             | 054                 |

| 100V            | 23.5mΩ @ 4.5V            | 35A                 |

Schematic Diagram

#### 3. Package Marking and Ordering Information

| Part no.   | Marking | Package | PCS/Reel | PCS/CTN. |

|------------|---------|---------|----------|----------|

| WX024N10PA | 024N10  | PDFN5X6 | 5,000    | 50,000   |

#### 4.Absolute Max Ratings at Ta=25°C (Note1)

| Parameter                       | Symbol          | Maximum     | Units |

|---------------------------------|-----------------|-------------|-------|

| Drain to Source Voltage         | $V_{DSS}$       | 100         | V     |

| Gate to Source Voltage          | $V_{GSS}$       | ±20         | V     |

| Drain Current (DC)              | $I_D$           | 35          | Α     |

| Drain Current (Pulse), PW≤300μs | I <sub>DP</sub> | 140         | Α     |

| Total Dissipation               | $P_{D}$         | 104.2       | W     |

| Avalanche Energy, Single Pulsed | E <sub>AS</sub> | 138         | mJ    |

| Junction Temperature            | T <sub>j</sub>  | 150         | °C    |

| Storage Temperature             | $T_{stg}$       | -55 to +150 | °C    |

Note 1: Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

## 5. Thermal Resistance Ratings (Note 2)

| Parameter        | Symbol         | Value | Unit |

|------------------|----------------|-------|------|

| Junction to Case | $R_{	heta JC}$ | 1.2   | °C/W |

Note 2: When mounted on 1 inch square copper board  $t \le 10$ sec The value in any given application depends on the user's specific board design.

#### 6.Electrical Characteristics at Ta=25°C (Note 3)

| Parameter                         | Symbol               | Test Conditions                              | Min. | Тур. | Max. | Units |

|-----------------------------------|----------------------|----------------------------------------------|------|------|------|-------|

| Drain to Source Breakdown Voltage | V <sub>(BR)DSS</sub> | $I_D = 250 \mu A, V_{GS} = 0 V$              | 100  | -    | -    | V     |

| Zero-Gate Voltage Drain Current   | I <sub>DSS</sub>     | V <sub>DS</sub> = 100V, V <sub>GS</sub> = 0V | -    | -    | 1    | μA    |

| Gate to Source Leakage Current    | I <sub>GSS</sub>     | $V_{GS} = \pm 20V, V_{SS} = 0V$              | ı    | -    | ±100 | nA    |

| Gate Threshold Voltage            | $V_{GS(th)}$         | $V_{DS}=V_{GS}$ , $I_{DS}=250\mu A$          | 1.0  | 1.5  | 2.5  | V     |

| Static Drain to Source On-State   | D                    | $I_D = 20A, V_{GS} = 10V$                    |      | 21.8 | 28   | mΩ    |

| Resistance                        | R <sub>DS(on)</sub>  | $I_D = 10A, V_{GS} = 4.5V$                   | -    | 23.5 | 33   | mΩ    |

| Input Capacitance                 | C <sub>iss</sub>     | V <sub>GS</sub> =0V,                         | -    | 2995 | -    | pF    |

| Output Capacitance                | $C_{oss}$            | V <sub>DS</sub> =40V,                        | -    | 111  | -    | pF    |

| Reverse Transfer Capacitance      | C <sub>rss</sub>     | Frequency=1.0MHz                             | 1    | 93   | -    | pF    |

| Turn-ON Delay Time                | t <sub>d(on)</sub>   | V <sub>DD</sub> = 50V,                       | ı    | 10   | -    | ns    |

| Rise Time                         | t <sub>r</sub>       | $I_D = 20A,$                                 | -    | 24   | -    | ns    |

| Turn-OFF Delay Time               | t <sub>d(off)</sub>  | $V_{GS} = 10V$ ,                             | -    | 63   | -    | ns    |

| Fall Time                         | t <sub>f</sub>       | $R_{GEN} = 3\Omega$                          | -    | 45   | -    | ns    |

|                                   | $Q_g$                | V <sub>DS</sub> = 50V,                       | -    | 72   | -    | nC    |

| Total Gate Charge                 | Q <sub>gs</sub>      | V <sub>GS</sub> =0 to 10V,                   | -    | 11   | -    | nC    |

|                                   | $Q_{gd}$             | I <sub>D</sub> = 20A                         | -    | 19   | -    | nC    |

| Diode Forward Voltage             | $V_{FSD}$            | I <sub>S</sub> = 20A, V <sub>GS</sub> = 0V   | 0.5  | -    | 1.2  | V     |

Note 3: Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

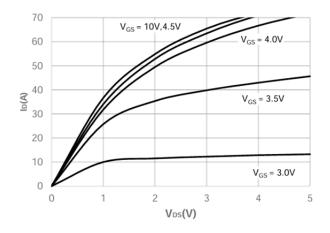

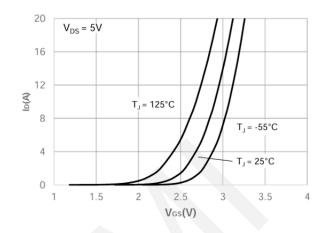

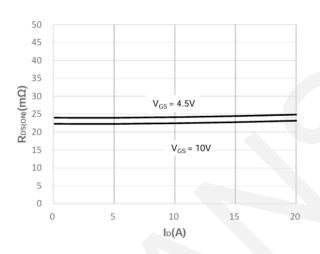

### 7. Typical electrical and thermal characteristics

**Output Characteristics**

Typical Transfer Characteristics

On-resistance vs. Drain Current

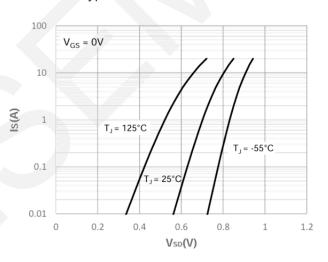

**Body Diode Characteristics**

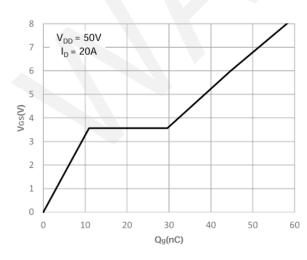

Gate Charge Characteristics

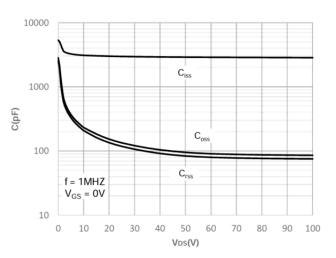

Capacitance Characteristics

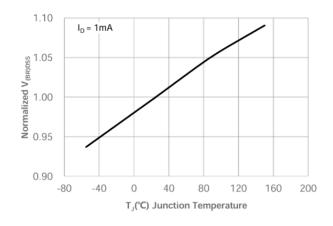

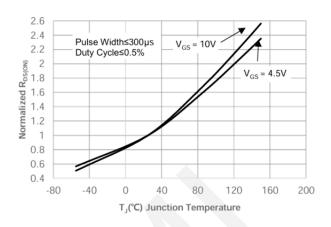

#### Normalized on Resistance vs.

Junction Temperature

Normalized on Resistance vs.

Junction Temperature

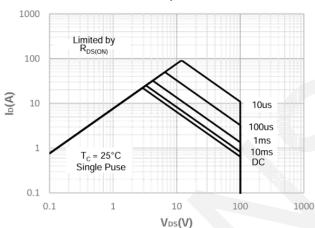

Maximum Safe Operating Area

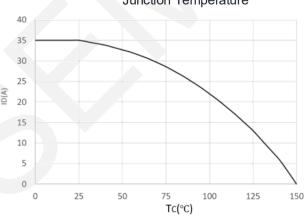

Maximum Continuous Drain Current vs.Case Temperature

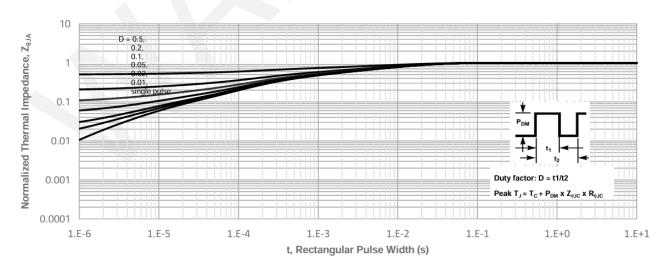

Maximum Effective Transient Thermal Impedance, Junction-to-Case

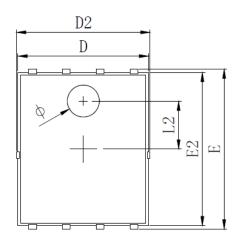

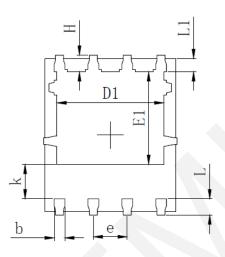

## 8.Package Dimensions

| SYMBOL |                      | MILLIMETER  |        |  |

|--------|----------------------|-------------|--------|--|

| SIMDUL | MIN                  | Тур.        | MAX    |  |

| A      | 0. 900               | 1.000       | 1. 100 |  |

| A1     |                      | 0. 254 REF. |        |  |

| A2     |                      | 0~0. 05     |        |  |

| D      | 4. 824               | 4. 900      | 4. 976 |  |

| D1     | 3. 910               | 4. 010      | 4. 110 |  |

| D2     | 4. 924               | 5. 000      | 5. 076 |  |

| E      | 5. 924               | 6. 000      | 6. 076 |  |

| E1     | 3. 375               | 3. 475      | 3. 575 |  |

| E2     | 5. 674               | 5. 750      | 5. 826 |  |

| b      | 0. 350 0. 400 0. 450 |             |        |  |

| е      |                      | 1.270 TYP.  |        |  |

| L      | 0. 534               | 0. 610      | 0. 686 |  |

| L1     | 0. 424               | 0. 500      | 0. 576 |  |

| L2     | 1.800 REF.           |             |        |  |

| k      | 1. 190               | 1. 290      | 1. 390 |  |

| Н      | 0. 549               | 0. 625      | 0. 701 |  |

| θ      | 8°                   | 10°         | 12°    |  |

| ф      | 1. 100               | 1. 200      | 1. 300 |  |

| d      |                      |             | 0. 100 |  |

#### 9. Important Notice

WAN SEMICONDUCTOR (NINGBO) CO.,LTD reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services and to discontinue any product or service. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to WANSEMI's terms and conditions of sale supplied at the time of order acknowledgment.

WANSEMI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in WANSEMI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent WANSEMI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

WANSEMI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using WANSEMI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

No WANSEMI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Unless WANSEMI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use, WANSEMI will not be responsible for any failure of such components to meet such requirements.